- #Modelsim simulation steps software

- #Modelsim simulation steps code

- #Modelsim simulation steps simulator

Optional.Īdvances the simulator the appropriate number of timesteps corresponding to 10.4 milliseconds.

#Modelsim simulation steps code

Specifies that VHDL procedures, functions and Verilog tasks are to be executed but treated as simple statements instead of entered and traced line by line. my design including a M4 processor and some BRAM used for boot and code region, I use the verilog file for simulation using VCS.

Steps the simulator to the next HDL statement. The different steps to follow to be able to customize the Wave View window panel in ModelSim when running the simulation flow in the Altera Quartus. Optional.Ĭauses the simulator to run to the next event time. A run -continue command may be input manually or used as the last command in a bp command string. Optional.Ĭontinues the last simulation run after a step command, step -over command or a breakpoint. Time steps and time units may also be set with the RunLength and UserTimeUnit variables in the modelsim.ini file.Ĭauses the simulator to run the current simulation forever, or until it hits a breakpoint or specified break event. The HDL Cosimulation block cosimulates a hardware component by applying input signals to and reading output signals from an HDL model under simulation in ModelSim. This chapter guides you through the basic steps for setting up an HDL Verifier session that uses Simulink ® and the HDL Cosimulation block to verify an HDL model. See "Setting default simulation options". Verify HDL Module with Simulink Test Bench Tutorial Overview. With the simulation time to solve the problems of the day, any step can not be wrong, of course, be wrong.

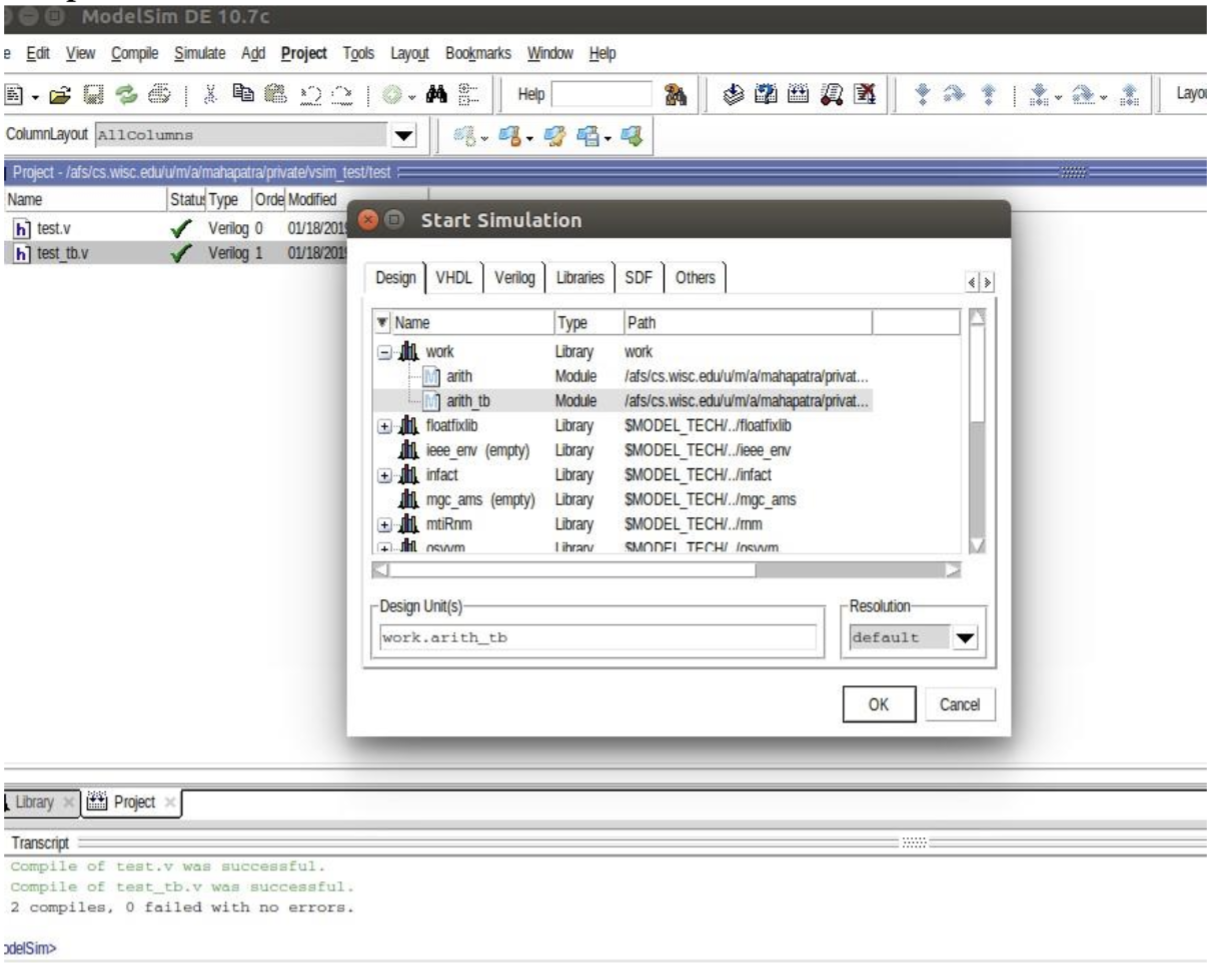

Go to File menu, select the change directory name to#Modelsim simulation steps software

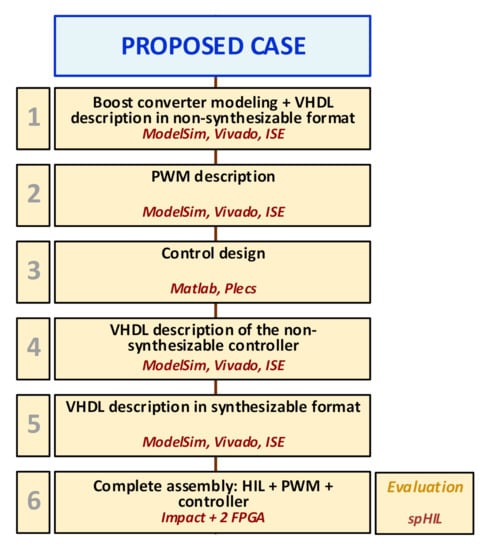

Step 1: Invoke Software and Change Directory. You can use these steps for the ModelSim-Altera and ModelSim SE/PE software. ModelSim / Questa Core Graphic User Interface windows Shell commands Steps to invoke a simulation. To manually run simulation without using the Quartus® II NativeLink feature, perform the following steps. The default and specifications can be changed during a Model Sim session by selecting Options > Simulation (Main window). Create and simulate a mixed VHDL/Verilog design. To open altera-modelsim go to Tools > Simulation Tool > RTL Simulation. In addition, optional may be specified as: This tutorial will walk you through the steps of creating Verilog modules in. The number may be fractional, or may be specified absolute by preceding the value with the character Optional.

Specifies the number of timesteps for the simulation to run. (b) ModelSim SE Tutorial Version 5.5e, 22 Aug 01, Mentor Graphics (c) Lesson 2 Basic VHDL Simulation, Preparing the Simulation, Mentor Graphics, 22 Aug 01, pages T-18 to T-23 SETTING UNIX ENVIRONMENT (steps at the UNIX prompt) 1. The run command advances the simulation by the specified number of timesteps.

0 kommentar(er)

0 kommentar(er)